## INTEGRATED CIRCUITS

## DATA SHEET

## **UMA1014**

Low-power frequency synthesizer for mobile radio communications

Product specification Supersedes data of October 1991 File under Integrated circuits, IC03 October 1992

**UMA1014**

#### **FEATURES**

- Single chip synthesizer; compatible with Philips cellular radio chipset

- · Fully programmable RF divider

- I<sup>2</sup>C interface for two-line serial bus

- On-chip crystal oscillator/TCXO buffer from 3 to 16 MHz

- 16 reference division ratios allowing 5 to 100 kHz channel spacing

- 1/8 crystal frequency output

- · On-chip out-of-lock indication

- Two extra VCO control outputs

- · Latched synthesizer alarm output

- Status register including out-of-lock indication and power failure

- Power-down mode.

### **APPLICATIONS**

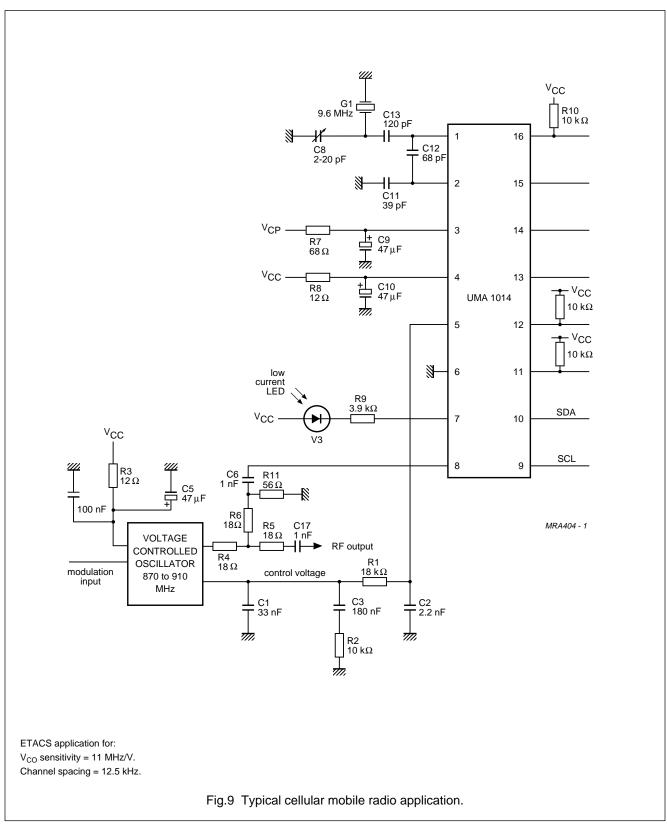

- Cellular mobile radio (NMT, AMPS, TACS)

- Private mobile radio (PMR)

- Cordless telephones.

#### **GENERAL DESCRIPTION**

The UMA1014 is a low-power universal synthesizer which has been designed for use in channelized radio communication. The IC is manufactured in bipolar technology and is designed to operate at 5 to 100 kHz channel spacing with an RF input from 50 to 1100 MHz. The channel is programmed via a standard I<sup>2</sup>C-bus. A low-power sensitive RF divider is incorporated together with a dead-zone eliminated, 3-state phase comparator. The low-noise charge pump delivers 1 mA or 1/2 mA output current to enable a better compromise between fast switching and loop bandwidth. A power-down circuit enables the synthesizer to be set to idle mode.

#### **QUICK REFERENCE DATA**

| SYMBOL                            | PARAMETER                            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|--------------------------------------|------|------|------|------|

| V <sub>CC</sub> , V <sub>CP</sub> | supply voltage range                 | 4.5  | 5.0  | 5.5  | V    |

| I <sub>CC</sub> + I <sub>CP</sub> | supply current                       | _    | 13   | _    | mA   |

| I <sub>CCpd</sub>                 | I <sub>CC</sub> in power-down        | _    | 2.5  | _    | mA   |

| f <sub>ref</sub>                  | phase comparator reference frequency | 5    | _    | 100  | kHz  |

| f <sub>RF</sub>                   | RF input frequency                   | 50   | _    | 1100 | MHz  |

| T <sub>amb</sub>                  | operating ambient temperature range  | -40  | _    | 85   | °C   |

#### **ORDERING INFORMATION**

| TYPE NUMBER  |      | PACKAGE                                                    |          |  |  |  |  |  |  |

|--------------|------|------------------------------------------------------------|----------|--|--|--|--|--|--|

| I TPE NUMBER | NAME | DESCRIPTION                                                | VERSION  |  |  |  |  |  |  |

| UMA1014T     | SO16 | plastic small outline package; 16 leads; body width 3.9 mm | SOT109-1 |  |  |  |  |  |  |

2

October 1992

**UMA1014**

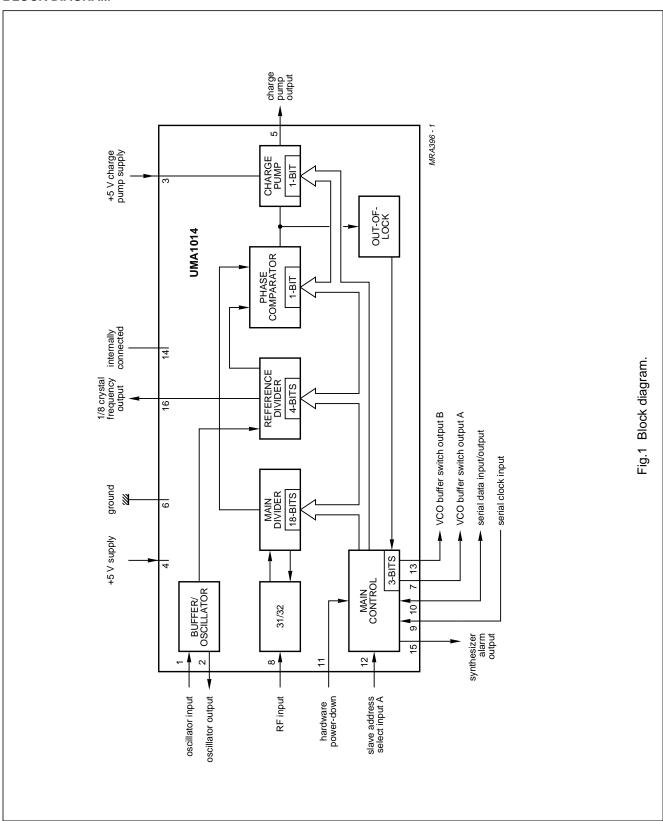

## **BLOCK DIAGRAM**

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

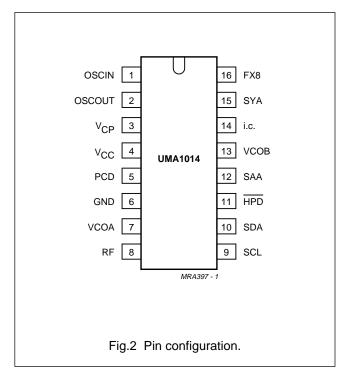

## **PINNING**

| SYMBOL          | PIN | DESCRIPTION                                        |

|-----------------|-----|----------------------------------------------------|

| OSCIN           | 1   | oscillator or TCXO input                           |

| OSCOUT          | 2   | oscillator output                                  |

| $V_{CP}$        | 3   | 5 V charge pump supply                             |

| V <sub>CC</sub> | 4   | 5 V supply                                         |

| PCD             | 5   | charge pump output                                 |

| GND             | 6   | ground                                             |

| VCOA            | 7   | VCO buffer switch output A (including out-of-lock) |

| RF              | 8   | RF input                                           |

| SCL             | 9   | serial clock input                                 |

| SDA             | 10  | serial data input/output                           |

| HPD             | 11  | hardware power-down (active LOW)                   |

| SAA             | 12  | slave address select input A                       |

| VCOB            | 13  | VCO buffer switch output B                         |

| i.c.            | 14  | internally connected                               |

| SYA             | 15  | synthesizer alarm output                           |

| FX8             | 16  | 1/8 crystal frequency output                       |

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

#### **FUNCTIONAL DESCRIPTION**

The UMA1014 is a low-power frequency synthesizer for radio communication which operates in the 50 to 1100 MHz range. The device includes an oscillator/buffer circuit, a reference divider, an RF divider, a 3-state phase comparator, a charge pump and a main control circuit to transfer the serial data into the four internal 8-bit registers. The  $V_{CC}$  supply feeds the logic part, the  $V_{CP}$  supply feeds the charge-pump only. Both supplies are +5 V (±10%). The power-down facility puts the synthesizer in the idle mode (all current supplies are switched off except in the control part). This allows any  $I^2C$  transfer and all information in the registers is retained thus enabling fast power-up.

#### Main divider

The main divider is a pulse swallow type counter which is fully programmable. After a sensitive input amplifier (50 mV, -13 dBm), the RF signal is applied to a 31/32 duo-modulus counter. The output is then used as the clock for the 5-bit swallow counter R = (MD4 to MD0) and the 13-bit main counter N = (MD17 to MD5). The ratio is transferred via the  $I^2$ C-bus to the registers B, C and D, and then buffered in an 18-bit latch. The ratio in the divider chain is updated with the new information when the least significant bit is received (i.e. D0). This update is synchronized to the output of the divider in order to limit the phase error during small jumps of the synthesized frequency.

The main divider can be programmed to any value between 2048 and 262143 (i.e.  $2^{18}$  –1). If ratio X, below 2048, is sent to the divider, the ratio (X + 2048) will be programmed. When it is required to switch between adjacent channels it is possible to program register D only, thus allowing shorter  $I^2C$  programming time.

### Oscillator

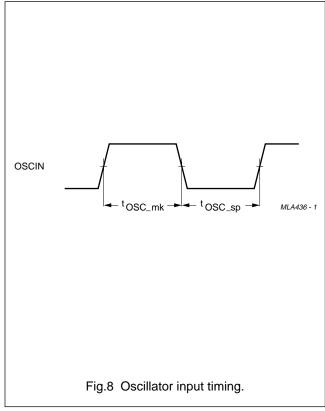

The oscillator is a common collector Colpitts type with external capacitive feedback. The oscillator has very small temperature drift and high voltage supply rejection. A TCXO or other type of clock can be used to drive the oscillator by connecting the source (preferably AC-coupled) to pin 1 and leaving pin 2 open-circuit. The oscillator acts as a buffer in this mode and requires no additional external components. The signal from the clock source should have a minimum space width of 31 ns.

#### Reference divider

The reference divider is semi-programmable with 16 division ratios which can be selected via the I<sup>2</sup>C-bus. The programming uses four bits of the register A (A3 to A0) as listed in Table 2. These ratios allow the use of a large number of crystal frequencies from 3 MHz up to 16 MHz. All main channel spacings can be obtained with a single crystal/TXCO frequency of 9.6 MHz.

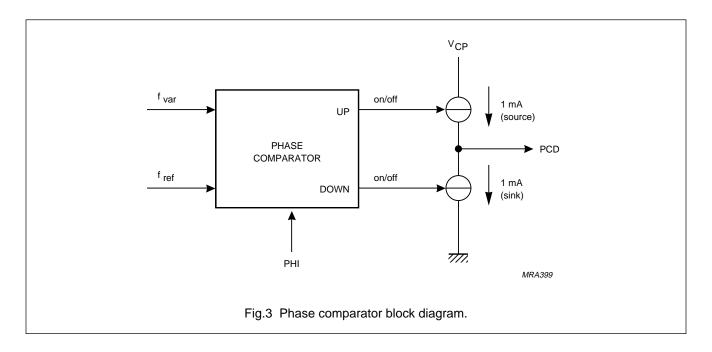

#### Phase comparator

A diagram of the phase comparator and charge pump is illustrated in Fig.3.

The phase comparator is both a phase and frequency detector. The detector comprises dual flip-flops together with logic circuitry to eliminate the dead-zone. When a phase error is detected the UP or DOWN signal goes HIGH. This switches on the corresponding current generator which produces a source or sink current for the loop filter. When no phase error is detected PCD goes high impedance. The final tuning voltage for the VCO is provided by the loop filter. The charge pump current is programmable via the I<sup>2</sup>C-bus. When IPCD (bit 5) is set to logic 1 the charge pump delivers 1 mA; when IPCD is set to logic 0 the charge pump delivers 0.5 mA.

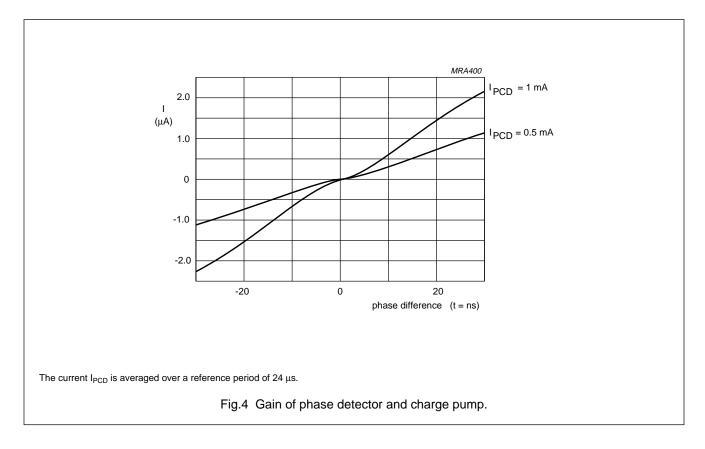

The phase comparator has a phase inverter logic input (PHI). This allows the use of inverted or non-inverted loop filter configurations. It is thus possible to use a passive loop filter which offers higher performances without an operational amplifier. The function of the phase comparator is given in Table 3 and a typical transfer curve is illustrated in Fig.4.

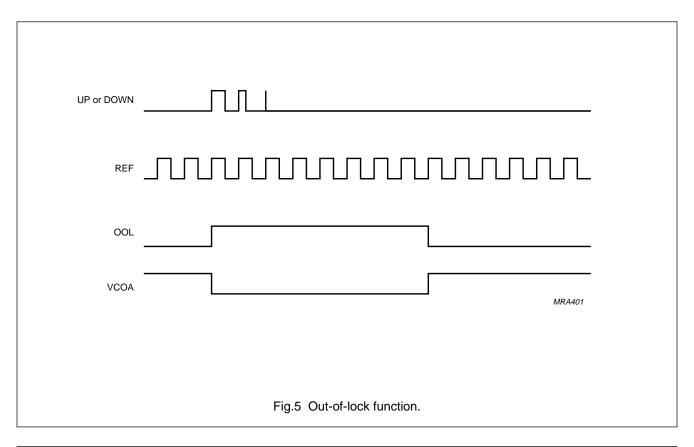

### **Out-of-lock detector**

An out-of-lock detector using the UP and DOWN signals from the phase comparator is included on-chip. The pin VCOA is an open collector output which is forced LOW during an out-of-lock condition. The same information is also available via the I<sup>2</sup>C-bus in the status register (bit OOL). When the phase error (measured at the phase comparator) is greater than approximately 200 ns, an out-of-lock condition is immediately flagged. The flag is only released after 6 reference cycles when the phase error is less than 200 ns.

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

Table 1 Division ratio in the main divider

|      | MAIN COUNTER: N |      |  |     |     |  |     | SWALL | OW COUN | ITER: R |

|------|-----------------|------|--|-----|-----|--|-----|-------|---------|---------|

| MD17 | MD16            | MD15 |  | MD8 | MD7 |  | MD5 | MD4   |         | MD0     |

| B1   | В0              | C7   |  | C0  | D7  |  | D5  | D4    |         | D0      |

| MSB  |                 |      |  |     |     |  |     |       |         | LSB     |

Table 2 Reference divider programming

| A3(RD3) | A2(RD2) | A1(RD1) | A0(RD0) | REFERENCE DIVISION<br>RATIO | CHANNEL SPACING FOR 9.6 MHz AT OSCIN |

|---------|---------|---------|---------|-----------------------------|--------------------------------------|

| 0       | 0       | 0       | 0       | 128                         | 75 kHz                               |

| 0       | 0       | 0       | 1       | 160                         | 60 kHz                               |

| 0       | 0       | 1       | 0       | 192                         | 50 kHz                               |

| 0       | 0       | 1       | 1       | 240                         | 40 kHz                               |

| 0       | 1       | 0       | 0       | 256                         | 37.5 kHz                             |

| 0       | 1       | 0       | 1       | 320                         | 30 kHz                               |

| 0       | 1       | 1       | 0       | 384                         | 25 kHz                               |

| 0       | 1       | 1       | 1       | 480                         | 20 kHz                               |

| 1       | 0       | 0       | 0       | 512                         | 18.75 kHz                            |

| 1       | 0       | 0       | 1       | 640                         | 15 kHz                               |

| 1       | 0       | 1       | 0       | 768                         | 12.5 kHz                             |

| 1       | 0       | 1       | 1       | 960                         | 10 kHz                               |

| 1       | 1       | 0       | 0       | 1024                        | 9.375 kHz                            |

| 1       | 1       | 0       | 1       | 1280                        | 7.5 kHz                              |

| 1       | 1       | 1       | 0       | 1536                        | 6.25 kHz                             |

| 1       | 1       | 1       | 1       | 1920                        | 5 kHz                                |

Table 3

Operation of the phase comparator

|                  | PHI = 0 (                           | PASSIVE LOOP                                                | FILTER) | PHI = 1                             | (ACTIVE LOOP                        | FILTER)             |

|------------------|-------------------------------------|-------------------------------------------------------------|---------|-------------------------------------|-------------------------------------|---------------------|

|                  | f <sub>ref</sub> < f <sub>var</sub> | $f_{ref} < f_{var}$ $f_{ref} > f_{var}$ $f_{ref} = f_{var}$ |         | f <sub>ref</sub> < f <sub>var</sub> | f <sub>ref</sub> > f <sub>var</sub> | $f_{ref} = f_{var}$ |

| UP               | 0                                   | 1                                                           | 0       | 1                                   | 0                                   | 0                   |

| DOWN             | 1                                   | 0                                                           | 0       | 0                                   | 1                                   | 0                   |

| I <sub>pcd</sub> | −1 mA                               | 1 mA                                                        | < ±5 nA | 1 mA                                | −1 mA                               | < ±5 nA             |

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

#### **MAIN CONTROL**

The control part consists mainly of the I<sup>2</sup>C-bus control interface and a set of four registers A, B, C and D. The serial input data (SDA) is converted into 8-bit parallel words and stored in the appropriate registers. The data transmission to the synthesizer is executed in the burst mode with the following format:

//slave addr./subaddr./data1/data2/.../datan//; n up to 4

Data byte 1 is written in the register indicated by the subaddress. An auto-increment circuit, if enabled

(AVI = 1), then provides the correct addressing for the ensuing data bytes. Since the length of the data burst is not fixed, it is possible to program only one register or the whole set. The registers are structured in such a way so that the burst, for normal operation, is kept as short as possible. The bits that are only programmed during the set-up (reference division ratio, power-down, phase inversion and current on PCD) are stored in registers A and B.

In the slave address six bits are fixed, the remaining two bits depend on the application.

Table 4 Slave address

| 1 1 | 0 | 0 | 0 | 1 | SAA | R/W |

|-----|---|---|---|---|-----|-----|

|-----|---|---|---|---|-----|-----|

$\overline{SAA}$  is the slave address. When  $\overline{SAA}$  goes HIGH then  $\overline{SAA} = 0$ , when  $\overline{SAA}$  goes LOW then  $\overline{SAA} = 1$ . This allows the use of two UMA1014s on the same bus but using a different address.  $\overline{R/W}$  should be set to logic 0 when writing to the synthesizer or set to logic 1 when reading the status register.

The subaddress includes the register pointer, and sets the two flags related to the auto-increment (AVI) and the alarm disable (DI).

Table 5 Subaddress

| × | X | X | DI | AVI | X | SB1 | SB0 |

|---|---|---|----|-----|---|-----|-----|

|---|---|---|----|-----|---|-----|-----|

#### Where:

X = not used

DI (Disable Interrupt):

DI = 1 disables the alarm on SYA

DI = 0 enables the alarm.

AVI (Auto Value Increment):

AVI = 1 enables the automatic increment

AVI = 0 disables the auto-increment.

SB1/SB0 are the pointers of the register where DATA1 will be written (see Table 6).

When the auto-increment is disabled (AVI = 0), the subaddress pointer will maintain the same value during the  $I^2C$ -bus transfer. All the data bytes will then be written consecutively in the register pointed by the subaddress.

**Table 6** Pointer of the registers

| SB1 | SB0 | REGISTER POINTED |

|-----|-----|------------------|

| 0   | 0   | A                |

| 0   | 1   | В                |

| 1   | 0   | С                |

| 1   | 1   | D                |

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

### Status register and synthesizer alarm

When an out-of-lock condition or a power dip occurs, SYA, which is an open collector output, is forced LOW and latched. The pin SYA will be released after the status register is read via the I<sup>2</sup>C-bus.

The status register contains the following information:

Table 7

Status register

| 0 | 0 | 0 | OOL | 0 | LOOL | LPD | DI |

|---|---|---|-----|---|------|-----|----|

### Where:

OOL = momentary out-of-lock

LOOL = latched out-of-lock

LPD = latched power dip

DI = disable interrupt (of the last write cycle).

The I<sup>2</sup>C-bus protocol to read this internal register is a single byte without subaddressing:

//slave address (R/ $\overline{W}$  = 1)/status register (read)//

Table 8 Bit allocation

| REGISTER | POINTER |      | BIT ALLOCATION |      |      |      |      |      |      | PRESET   |

|----------|---------|------|----------------|------|------|------|------|------|------|----------|

|          |         | 7    | 6              | 5    | 4    | 3    | 2    | 1    | 0    |          |

| Α        | 00      | PD   | Х              | IPCD | Х    | RD3  | RD2  | RD1  | RD0  | 00001110 |

| В        | 01      | 1    | 0              | 1    | PHI  | VCOB | VCOA | MD17 | MD16 | 10100101 |

| С        | 10      | MD15 | MD14           | MD13 | MD12 | MD11 | MD10 | MD9  | MD8  | 00111000 |

| D        | 11      | MD7  | MD6            | MD5  | MD4  | MD3  | MD2  | MD1  | MD0  | 10000000 |

Where X = not used

Table 9 Register allocation

| REGISTER<br>NAME | BIT NAME    | FUNC                             | PRESET<br>VALUE                       |                        |

|------------------|-------------|----------------------------------|---------------------------------------|------------------------|

| Α                | PD          | power down                       | PD = 0 normal operation               | 0                      |

|                  | IPCD        | programmable charge pump current | IPCD = 1 = 1 mA;<br>IPCD = 0 = 0.5 mA | 0                      |

|                  | RD3RD0      | reference ratio                  | see Table 2                           | 1110; r = 1536         |

| В                | PHI         | phase inverter                   | PHI = 0 passive loop filter           | 0                      |

|                  | VCOA        | VCO switch A                     | set pin 7                             | 1                      |

|                  | VCOB        | VCO switch B                     | set pin 13                            | 0                      |

|                  | MD17, MD16  | bits 17 and 16                   | MSB of main divider ratio             | 01                     |

| С                | MD15 to MD8 | bits 15 to 8                     | main divider ratio                    | 00111000               |

| D                | MD7 to MD0  | bits 7 to 0                      | main divider ratio                    | 10000000;<br>r = 80000 |

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

### **LIMITING VALUES**

In accordance with the Absolute Maximum System (IEC 134).

| SYMBOL           | PARAMETER                           | MIN. | MAX.            | UNIT |

|------------------|-------------------------------------|------|-----------------|------|

| V <sub>CC</sub>  | supply voltage range                | -0.3 | 7.0             | V    |

| Vi               | voltage range to ground (all pins)  | 0    | V <sub>CC</sub> | V    |

| T <sub>stg</sub> | IC storage temperature range        | -55  | +125            | °C   |

| T <sub>amb</sub> | operating ambient temperature range | -40  | +85             | °C   |

### **HANDLING**

Every pin referenced to ground withstands ESD (HMB) tests in accordance with MIL-STD-883C method 3015 class 2. Inputs and outputs are protected against electrostatic discharges in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling Integrated Circuits.

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

## **CHARACTERISTICS**

$T_{amb}$  = 25  $^{\circ}C;\,V_{CC}$  = 4.5 to 5.5 V; unless otherwise specified.

| SYMBOL                | PARAMETER                                    | CONDITIONS               | MIN.     | TYP. | MAX.                 | UNIT |

|-----------------------|----------------------------------------------|--------------------------|----------|------|----------------------|------|

| Supply (pir           | ns V <sub>CC</sub> and V <sub>CP</sub> )     |                          |          | '    |                      | •    |

| V <sub>CC</sub>       | supply voltage range                         |                          | 4.5      | _    | 5.5                  | V    |

| I <sub>CC</sub>       | supply current                               |                          | _        | 11.5 | 13.5                 | mA   |

| I <sub>CCpd</sub>     | supply current                               | power-down               | _        | 2.5  | 3.3                  | mA   |

| V <sub>CP</sub>       | charge pump supply voltage                   |                          | 4.5      | _    | 5.5                  | V    |

| I <sub>CP</sub>       | charge pump supply current                   | IPCD = 0.5 mA            | _        | 1.4  | 1.8                  | mA   |

| I <sub>CPpd</sub>     | charge pump supply current                   | power-down               | _        | 0.01 | _                    | mA   |

| RF dividers           | s (pin RF)                                   |                          |          |      |                      | •    |

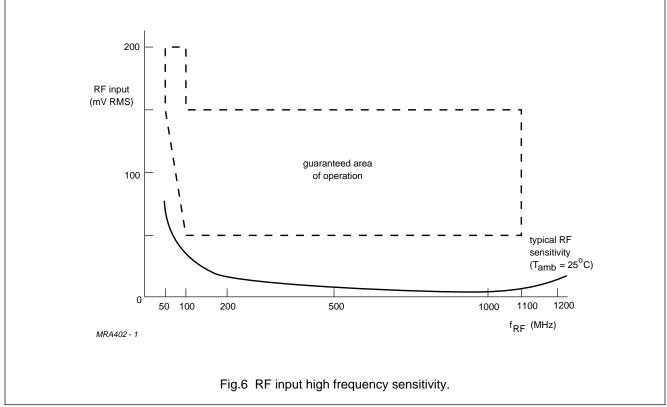

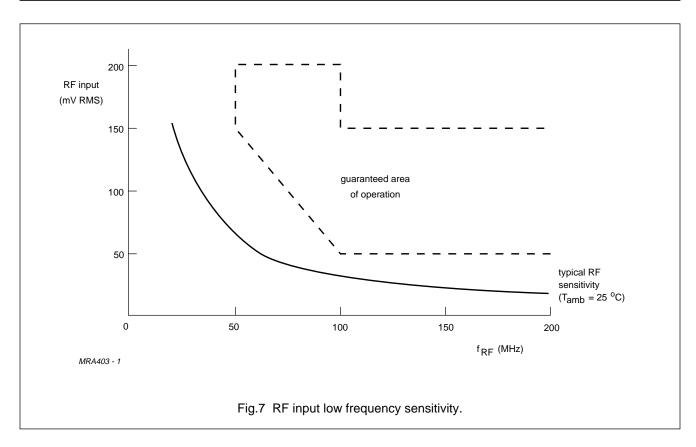

| f <sub>RF</sub>       | frequency range                              |                          | 50       | _    | 1100                 | MHz  |

| V <sub>RF(rms)</sub>  | input voltage level (RMS value)              | 50 to 100 MHz            | 150      | _    | 200                  | mV   |

| ,                     |                                              | 100 to 1100 MHz          | 50       | _    | 150                  | mV   |

| R <sub>I</sub>        | input resistance                             | at 1 GHz                 | _        | 200  | _                    | Ω    |

|                       |                                              | at 100 MHz               | _        | 600  | _                    | Ω    |

| Cı                    | input capacitance                            | note 1                   | _        | 2.0  | _                    | pF   |

| R <sub>RF</sub>       | division ratios                              |                          | 2048     | _    | 262143               | Ī-   |

| Oscillator a          | and reference divider (pins OSCIN            | and OSCOUT)              | '        |      |                      | !    |

| fosc                  | oscillator frequency range                   |                          | 3        | _    | 16                   | MHz  |

| V <sub>OSC(RMS)</sub> | input level sine wave (RMS value)            |                          | 0.15     | _    | V <sub>CC</sub> /2.8 | V    |

| V <sub>OSC(p-p)</sub> | input level square wave (peak-to-peak value) |                          | 0.45     | _    | V <sub>CC</sub>      | V    |

| t <sub>OSC_mk</sub>   | input mark width                             | see Fig.8                | 10       | _    | _                    | ns   |

| t <sub>OSC_sp</sub>   | input space width                            |                          | 31       | _    | _                    | ns   |

| Z <sub>OSC</sub>      | output impedance at pin<br>OSCOUT            |                          | -        | _    | 2                    | kΩ   |

| R <sub>ref</sub>      | reference division ratio                     | see Table 1              | 128      | _    | 1920                 |      |

| 1/8 crystal           | frequency (open collector output)            | (pin FX8)                | <u>'</u> |      |                      |      |

| I <sub>OL</sub>       | LOW level output current                     | V <sub>OL</sub> ≥ 0.6 V  | 1.0      | _    | _                    | mA   |

| Phase com             | parator (pin PCD)                            |                          | <u>'</u> |      |                      | •    |

| f <sub>PCD</sub>      | frequency range                              |                          | 5        | _    | 100                  | kHz  |

| I <sub>PCD</sub>      | output current                               | V <sub>PCD</sub> = 2.5 V |          |      |                      |      |

|                       |                                              | bit IPCD = 1             | 0.9      | 1.2  | 1.4                  | mA   |

|                       |                                              | bit IPCD = 0             | 0.45     | 0.6  | 0.75                 | mA   |

| I <sub>PCDL</sub>     | output leakage current                       |                          | -5       | ±1   | +5                   | nA   |

| V <sub>PCD</sub>      | output voltage                               |                          | 0.4      | _    | V <sub>CP</sub> -0.5 | V    |

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

| SYMBOL            | PARAMETER                           | CONDITIONS              | MIN.         | TYP.  | MAX. | UNIT |

|-------------------|-------------------------------------|-------------------------|--------------|-------|------|------|

| Serial clock      | c and serial data input (pins SCL a | and SDA)                | -            | •     |      | •    |

| f <sub>CLK</sub>  | clock frequency                     |                         | 0            | _     | 100  | kHz  |

| V <sub>IH</sub>   | HIGH level input voltage            |                         | 3            | _     | _    | V    |

| V <sub>IL</sub>   | LOW level input voltage             |                         | _            | _     | 1.5  | V    |

| I <sub>IH</sub>   | HIGH level input current            |                         | _            | 3     | 10   | μΑ   |

| I <sub>IL</sub>   | LOW level input current             |                         | -10          | -5    | _    | μΑ   |

| Cı                | input capacitance                   |                         | _            | _     | 10   | pF   |

| I <sub>sink</sub> | SDA sink current                    | V <sub>OL</sub> = 0.4 V | 3            | _     | _    | mA   |

| Slave addre       | ess select input (pin SAA) and Ha   | rdware power-down inpu  | ıt (pin HPD  | N)    |      |      |

| V <sub>IH</sub>   | HIGH level input voltage            |                         | 3            | _     | _    | V    |

| V <sub>IL</sub>   | LOW level input voltage             |                         | _            | _     | 0.4  | V    |

| I <sub>IH</sub>   | HIGH level input current            |                         | _            | _     | 0.1  | μΑ   |

| I <sub>IL</sub>   | LOW level input current             |                         | -10          | _     | _    | μΑ   |

| VCO outpu         | t switches (pins VCOA and VCOB      | ) and synthesizer alarm | (pin SYA); r | note2 |      |      |

| I <sub>OL</sub>   | LOW level sink current              | V <sub>OL</sub> ≥ 0.4 V | 400          | _     | _    | μΑ   |

|                   |                                     |                         |              |       |      |      |

### **Notes**

- 1. C<sub>I</sub> is in parallel with R<sub>I</sub>.

- 2. Pin VCOA is forced to logic 0 during out-of-lock condition.

**UMA1014**

# Low-power frequency synthesizer for mobile radio communications

**UMA1014**

**UMA1014**

### **APPLICATION INFORMATION**

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

0.3

0.028

0.012

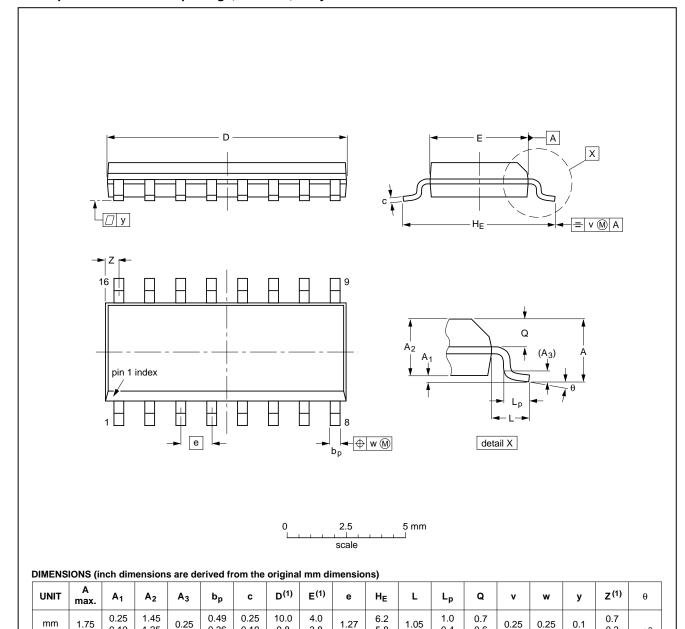

### **PACKAGE OUTLINE**

SO16: plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

#### Note

inches

0.069

0.10

0.0098

0.0039

1.25

0.057

0.049

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

0.01

0.36

0.019

0.014

0.19

0.0098

0.0075

9.8

0.39

0.38

3.8

0.16

0.15

| OUTLINE  | REFERENCES |          |      | EUROPEAN   | ISSUE DATE                      |

|----------|------------|----------|------|------------|---------------------------------|

| VERSION  | IEC        | JEDEC    | EIAJ | PROJECTION | ISSUE DATE                      |

| SOT109-1 | 076E07S    | MS-012AC |      |            | <del>91-08-13</del><br>95-01-23 |

0.050

5.8

0.24

0.23

0.041

0.4

0.039

0.016

0.028 0.020

0.01

0.01

0.004

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

#### **SOLDERING**

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

### Reflow soldering

Reflow soldering techniques are suitable for all SO packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at  $45 \,^{\circ}\text{C}$ .

### Wave soldering

Wave soldering techniques can be used for all SO packages if the following conditions are observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow.

- The package footprint must incorporate solder thieves at the downstream end.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### Repairing soldered joints

Fix the component by first soldering two diagonally-opposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300  $^{\circ}$ C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320  $^{\circ}$ C.

#### **DEFINITIONS**

| data about contains target or goal ensaifications for product development        |

|----------------------------------------------------------------------------------|

| data sheet contains target or goal specifications for product development        |

| data sheet contains preliminary data; supplementary data may be published later. |

| data sheet contains final product specifications.                                |

| C                                                                                |

### **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **Application information**

Where application information is given, it is advisory and does not from part of the specification.

## Low-power frequency synthesizer for mobile radio communications

**UMA1014**

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.